# 5. Citisia 2009

by Jatmiko Endro Suseno

**Submission date:** 19-Feb-2020 08:35AM (UTC+0700)

**Submission ID: 1259856014**

File name: 5.CITISIA\_2009.docx (82.7K)

Word count: 2737

Character count: 14559

## Artificial Intelligence Techniques for SPICE Optimization of MOSFET Modeling

Abstract—This paper proposes new method for optimize and verified electric characterization graph of MOSFET by using artificial neural network. Optimization using Neural Network (ONN) will compare current-voltage (I-V) Characteristic graph between the TCAD simulation and TSPICE 5 deling as desire data control a model parameter of BSIM. In this paper, the neural network method is dynamic feedforward Neural Network. After NN training, the best result is at Neural Network architecture of 36-30-10-5 with Mean Squared Error (MSE) of 1e-28 at epoch of 5.

Submicron CMOS technology appears to be a feasible and cost-effective integration solution for electronics device systems. Effectively, the maturity of silicon-based CMOS technology for small device feature size and low voltage digital circuits and also the recent progresses of MOSFETs performances. A model will help us to understand the

I. INTRODUCTION

meaning of some of the parameters that appear in its mathematical model.

Besides the physical parameters often introduces nonphysical parameters that do not necessarily need to correspond to some physical parameter. Such nonphysical parameters often combine the effects of one or more physical effects. Each MOSFET model is characterized with a set of parameters and these parameters have to be estimated if they cannot be measured either easily or not at all. The process of estimating model parameters is called parameter extraction and a brief description of various optimization methods that can be used to control the progress of a parameter extraction algorithm follows.

Parameters of MOSFET model may represent component

values such as the width and length of MOSFETs, or any other quantities that are fixed by the particular choice of circuit design and manufacturing process, but that may, at least in principle, be adapted to optimize circuit or device performance. Constants of nature, such as the speed of light or the boltzmann constant, are therefore not considered as parameters.

Existing approaches for transistor modeling are based on lumped equivalent circuits. The equivalent circuit approach involves determination of an equivalent circuit topology and formulation of the circuit elements. Such an approach not only reconstruction of the circuit elements and ifficult trial and process. As the drain current depends of the drain-to-source, Vd and gate-to-source, Vg, bias voltages, it was implemented into SPICE as a voltage-controlled current source.

Artificial Neural Network (ANN) has been recognize as a powerful tool for modeling and optimization problems[1]. Therefore, this paper proposes ANN method for modeling and optimization of current-voltage (I-V) characterization 1 tween the TCAD Simulation and TSPICE modeling. The universal approximation property of ANN provides themthe ability to learn any arbitrarily nonlinear input-output relationships [2] from corresponding measured or simulated data for investigating NN approaches to model transistor DC [3], small signal [4], and large-signal [5] behaviors and also presents possible ways to continue extract some other circuit value such as parasitic capacitance, time delay and speed performance.

#### II. THEORY

A. MSFET Device

The Metal Oxide Substrate Field Effect Transistor (MOSFET) is the first transistor type ever manufactured and is the most common FET transistor.

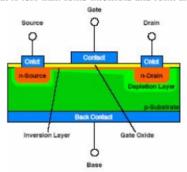

Fig. 1 shows N-MOSFET transistor which consists of n-type semiconductor material and its channel is made of p-type material. N-type semiconductor materials are based on a doping process which adds certain types of atoms to the semiconductor to increase the number of free negative mobility carriers — electrons. The process of n-type doping produces an abundance of electrons in the material and therefore electrons carry the charge. If we start with all voltages grounded and apply a positive voltage at gate (V<sub>GS</sub>), an electric field is created. This forces electrons move towards the gate oxide pushing out holes. Since the gate

.

oxide is an insulator, electrons cannot pass through for a voltage that is less than some threshold and form an electric

Fig. 1. MOSFET Device

field known as the "Inversion Layer" which connects the drain and source and closes the electric circuit. Electric current can now flow from in between source and drain and moreover drain (or source) can supply more electrons. The current gain capability of a Field-Effect-Transistor (FET) is easily explained by the fact that no gate current is required to maintain the inversion layer and the resulting current between drain and source. The device has therefore an infinite current gain in DC. The current gain is inversely proportional to the signal frequency, reaching unity current gain at the transit frequency. The voltage gain of the MOSFET is caused by the fact that the current saturates at higher drain-source voltages, so that a small drain current variation can cause a large drain voltage variation [6].

#### B. MOSFET Modeling

Vgs (gate-source voltage) controls the value of Ibs (drainsource current) thus how much current flows in between drain and source by creating an inversion layer (electric field) which connects the circuit in between drain and source. Ins and VGs together with VDs (drain-source voltage) and VBs (base-source voltage) control the shape of the inversion layer and are the only variables we measure. The value of IDS is transformed by means of a mathematical model where take all information that we know and with the use of mathematical modeling construct a function which presents the dependency. The large signal currents of the ID VDs plane are calculated from the expression:

$$I_G = I_B = 0 \tag{1}$$

$$\star I_{CUTOFF}, \qquad V_{GS} < V_{TH}$$

(2)

Where it is assumed that the drain and source are designated so that  $V_{DS} \ge 0$ .  $V_{DSAT}$  is a parameter that characterizes the transition between the ohmic and saturation regions.

Operation in Quadrant 3 of the ID- VDS plane is characterized by the same equations, where the drain and source designations are internally made so that V<sub>DS</sub> ≥ 0.[7] The device element line (card) in the SPICE deck contains information about the nodal location of the device in the circuit as well as geometrical information about the device and optional initial condition variables. In the device element line, reference is made to a specific device model. The .MODEL line (card) in the SPICE deck contains generic information about the electrical characteristics of device formed in a process based upon the characterizing process parameters. Each device has a separate device element line. Typically, many devices will reference a single .MODEL line.

#### C. Optimization Methods

In order to be able to classify parameter extraction methods, brief information about the methods and heuristics that are used to obtain mathematical model parameters and/or control the progress of the parameter extraction algorithm are necessary. This overview is also necessary because the following methods either already have been used for parameter extraction or could 2 used in future. Parameter extraction of MOSFET model for each process technology start with an initial set of parameters that comes from, 1) Vendor supplied models. 2) Previous MOSFET models. 3) Extracted models from physical fundamentals. Interaction between parameters that are optimized in a given strategy is controlled by the maximum and minimum limit of each parameter. There are nine optimization strategies that are implemented such as Parameters in Threshold and 7 bthreshold Regions, Threshold Shift effect parameters, reshold Shift and Channel Resistance effects parameters, Threshold \$7 ft and Channel Resistance effects Binning parameters, Low Bias Drain Saturated Cu7ent parameters, Low Bias Output Resistance Parameters, High Bias Drain Saturated Current parameters, High Bias Output Resistance Parameters, and Juncti 2 Capacitance Parameters. All of strategies presented are a standard optimization strategy and it may vary from one technology to the other.[8]

#### D. Dynamic Feedforward Neural Network

Dynamic feedforward 5 ural networks are conceived as mathematical constructions, independent of any particular physical representation or interpretation. This section shows how these artificial neural networks can be related to device and subcircuit models that involve physical quantities like currents and voltages. Feedforward neural networks can,

under relatively mild conditions, be guaranteed to preserve monotonicity in the multidimensional static behaviour. With contemporary physical models, it is generally no longer possible to guarantee monotonicity, due to the complexity of the mathematical analysis needed to prove monotonicity. It is an important property, however, because many devices are known to have monotonic characteristics. A nonmonotonic model for such a device may yield multiple spurious

solutions for the circuit in which it is applied and it may lead to nonconvergence even during time domain circuit simulation. The monotonicity guarantee for neural networks can be maintained for highly nonlinear multidimensional behaviour, which so far has not been possible with table models without requiring excessive amounts of data. Furthermore, the monotonicity guarantee is optional, such that nonmonotonic static behaviour can still be modelled.

Figure 2. A dynamic feedforward neural network architecture.

14 eedforward neural network will be characterized by the number of layers 44d the number of neurons per layer. Layers are counted starting with the input layer as layer 0, such that a network with output layer K involves a total of K + 1 layers (which would have been 16 ayers in case one prefers not to count the input layer). Layer k by definition contains  $N_k$  neurons, where k = 0, ..., K. The number  $N_k$ may also be referred to as the width of layer k. Neurons that are not directly connected to the inputs or outputs of the network belong to a so-called hidden layer, of which there are K - 1 in a (K + 1)-layer network. Network inputs are labeled as  $x^{(0)} \equiv (x^{(0)}, \dots, x^{(0)})$ , and network outputs as (K) (K).,  $y_{Nk,k})^T$  represents the vector of neuron outputs for layer k, containing 4s its elements the output variable yi;k for each individual i uron i in layer k. The network inputs will be treated by a dummy neuron layer k = 0, with enforced neuron j outputs  $y_{j,0} \equiv x_j^{(0)}$ ,  $j = 0, ..., N_0$ . However, when counting the number of neurons in a network, we will not take the dummy input neurons into account. The logistic function  $F(s_{ik})$ , is strictly monotonically increasing in  $s_{ik}$ . However, we will generally use nonzero v's and  $\tau$ 's, and will instead of the logistic function apply other infinitely smooth  $(\mathbb{C}^{\infty})$  nonlinear modelling functions F. The standard logistic function lacks the common transition between highly nonlinear and weakly nonlinear behaviour that is typical for semiconductor devices and circuits.

$$F_{i}(s_{ik}, \delta_{ik}) = \frac{1}{\delta} \prod_{k=1}^{n} \frac{1}{\cosh} \frac{s_{ik} + \delta_{ik}}{1 + \ln \cosh} \frac{s_{ik} - \delta_{ik}}{1 + \ln \cosh}$$

$$= \frac{1}{\delta_{ik}} \ln \frac{\cosh \frac{s_{ik} + \delta_{ik}}{2}}{\cosh \frac{s_{ik} - \delta_{ik}}{2}}$$

$$(5)$$

with  $\delta ik \neq 0$

Preliminary experience with modeling MOSFET dc characteristics indicates that this helps to avoid unacceptable local minima in the error function (cost function) for optimization-unacceptable in the sense that the results show too gradual near-subthreshold transitions [9].

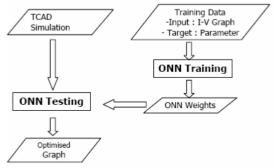

#### II. METHODOLOGY

The Artificial Neural Network method is that used for this optimization is called Optimization using Neural Network (ONN). The steps of ONN are showed at flow chart figure 3 below.

Figure 3. Optimization using Neural Network (ONN) Flow chart

The process used to fabricate the planar and vertical NMOS transistor will be simulated using TCAD Silvaco. It is used to create the device structure, adding dopant, defining electrodes and creating the mesh. The structure is that resulted follow parameter at Table I below.

After that, the results from the simulation using Silvaco-Atlas will get electrical characteristics such as Id-Vd, Id-Vg, C-V characteristics graph. In this paper, an only Id-Vd characteristic is that optimized. The result data of TCAD will be used as comparison data or optimization from ONN

TABEL I MOSFET DEVICE PARAMETER

| Parameter                     | Value                               |  |

|-------------------------------|-------------------------------------|--|

| Type                          | n-MOSFET                            |  |

| Body doping of Boron          | 9.10 <sup>17</sup> cm <sup>-3</sup> |  |

| Polysilicon doping of Arsenic | 1.10 <sup>15</sup> cm <sup>-3</sup> |  |

| Channel length (Lg)           | 150 nm                              |  |

| Oxide thickness (Tox)         | 5 nm                                |  |

method. The other hand, the electrical characteristics of 1OSFET can be obtained from SPICE. The ONN can be trained using such data to produce fast and accurate DC neuromodels. For this work, the training samples are collected 15  $\Gamma$ -SPICE simulations using BSIM3 according to 1.3  $\mu$ m technology. 11 n MOSFET length and width are 1.5  $\mu$ m and 3  $\mu$ m respectively. The device is fully characterized from gathered data with  $V_g$  is 1.1, 2.2 and 3.3 V, and  $V_d$  ranging from 0 to 3.3V. The I-V characteristic

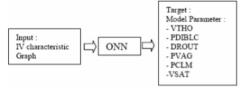

simulations were taken for the drain current Id. The each Id-Vd graph has physics value parameters, such as threshold voltage (VTHO), the drain induced barrier lowering (PDIBLC), L dependent coefficient of the DIBL effect in output resistance (DROUT), Gate dependence of early voltage (PVAG), channel length modulation (PCLM), and Drain saturation voltage (VSAT) parameters. If the parameters change then the graph will change according to what changed parameter. The parameter is called as data target. The pair of Id-Vd graph and physics parameter as ONN input and output respectively is showed at Figure 4 below.

Figure 4. Input-Target Data of the ONN method

#### TABLE II ARTIFICIAL NEURAL NETWORK PARAMETER

| Parame10                   | Value                        |  |  |

|----------------------------|------------------------------|--|--|

| Network Type               | Feed-Forward Backpropagation |  |  |

| Training Function          | Trainlm                      |  |  |

| Adaption Training Function | Learngdm                     |  |  |

| Error Function             | Mean Square Error            |  |  |

| 13 put Transfer Fuction    | Tansig                       |  |  |

| Hidden Transfer Function   | Tansig                       |  |  |

| Output Transfer Function   | Purelin                      |  |  |

More and more various pairs of input-target are more and better. The training sets were that used follow the table II above. Series of neural networks with different numbers of hidden neurons are trained using Levenberg Marquardt (trainlm) algorithm. The feed forward with various architectures was found to provide the best trade-off between the desired accuracy and the model complexity.

#### III. RESULT

The MOSFET device simulation using TCAD have gotten electrical parameter result that can be shown at table III below. This parameter is obtained with planar n 12 DSFET process parameter of substrate concentr 11 n, 9.10-17 cm<sup>-3</sup>, source and drain doping concentration, 1.10-15 cm<sup>-3</sup>, channel length (Lg), 150 nm and oxide thickness (tox), 5 nm.

TABEL III ELECTRIC PERFORMANCE RESULT OF MOSFET

| ELECTRIC PERFORMANCE RESULT OF MOSFET |                               |  |  |

|---------------------------------------|-------------------------------|--|--|

| 8 Parameter                           | Value                         |  |  |

| Threshold Voltage (Vth)               | 0.77 V                        |  |  |

| Leakage Current (Ioff)                | 1.36.10 <sup>-15</sup> (A/um) |  |  |

| Drive Current (Ion)                   | 8.06.10 <sup>-7</sup> (A/um)  |  |  |

| DIBL                                  | 44 (mV/V)                     |  |  |

| Subthreshold Slope (S)                | 82 (mV/decade)                |  |  |

With the MOSFET structure, the electric characteristic is used by SPICE model for optimizing process. Before and after Optimizing using Neural Network process of Id-Vd graphs can be described at figure 5 below.

Figure 5. Optimization method using Artificial Neural Network

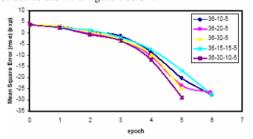

The ONN method used Neural Network process with its parameters was declared at table II. In this network type, it used the feed-forward backpropagation method because this method had the monotonicity guarantee for neural networks that could be maintained for input and target nonlinear multidimensional data, which so far had not been possible with table models without requiring excessive amounts of data. And also this method can avoid convergence problems, because it avoids the need for an iterative solver. The graph error can be shown at figure 6 below.

Figure 6. Training Performance of ONN process

The stabil 17 of feedforward neural networks can be guaranteed. The stability of feedforward neural networ 6 depends solely on the stability of its individual neurons. If all neurons are stable, then the feedforward network is also stable. For training process with various the network architectures, graphs of error training showed Mean Square Error (MSE) result that more and more reduce for all architectures.

The training Mean Squared Errors (MSEs) of all architectures are below of 1e-25 that was obtained after 5-6 iterations. The best result is at Neural Network architecture of 36-30-10-5 with Mean Square Error (MSE) of 1e-28 at epoch of 5.

#### IV. CONCLUSION

An alternative optimization method for optimize electric characterization graph of MOSFET between MOSFET model and measured/simulation using Neural Network was proposed. The conventional optimization method is trial and error method so that it need more time to achieve optimizing result. The Optimization using Neural Network (ON 5 has few steps and small error to obtained desire result. In this paper, the neural network method is dynamic feedforward

| Neural Network After NN training the best result is at                                                          |

|-----------------------------------------------------------------------------------------------------------------|

| Neural Network. After NN training, the best result is at<br>Neural Network architecture of 36-30-10-5 with Mean |

| Squared Error (MSE) of 1e-28 at epoch of 5.                                                                     |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

### 5. Citisia 2009

| 5. C    |                                                                                                                                                        |       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ORIGINA | ALITY REPORT                                                                                                                                           |       |

| SIMILA  | 8% 11% 15% 2% ARITY INDEX INTERNET SOURCES PUBLICATIONS STUDENT PA                                                                                     | APERS |

| PRIMAF  | RY SOURCES                                                                                                                                             |       |

| 1       | thescipub.com Internet Source                                                                                                                          | 7%    |

| 2       | ee.sharif.edu<br>Internet Source                                                                                                                       | 2%    |

| 3       | edoc.bib.ucl.ac.be:81 Internet Source                                                                                                                  | 1%    |

| 4       | Meijer, P. B. L "Neural Networks for Device<br>and Circuit Modelling", Lecture Notes in<br>Computational Science and Engineering, 2001.<br>Publication | 1%    |

| 5       | Hatti, M "Dynamic neural network controller model of PEM fuel cell system", International Journal of Hydrogen Energy, 200906 Publication               | 1%    |

| 6       | V. Ceperic, A. Baric, B. Pejcinovic. "Artificial neural network in modelling of voltage controlled oscillators with jitter", Proceedings of the 12th   | 1%    |

IEEE Mediterranean Electrotechnical

Conference (IEEE Cat. No.04CH37521), 2004

Publication

| 7  | "SPICE BSIM3 Model Parameter Extraction and Optimisation: Practical Considerations", International Journal of Electrical Engineering & Education, 2012 Publication                                                                                                | 1%  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8  | Submitted to Universiti Teknikal Malaysia<br>Melaka<br>Student Paper                                                                                                                                                                                              | 1%  |

| 9  | Submitted to Sophia University Student Paper                                                                                                                                                                                                                      | <1% |

| 10 | M. Camargo, D. Jimenez, L. Gallego. "Using of<br>Data Mining and Soft Computing Techniques for<br>Modeling Bidding Prices in Power Markets",<br>2009 15th International Conference on<br>Intelligent System Applications to Power<br>Systems, 2009<br>Publication | <1% |

| 11 | Chiyui Ahn, Mincheol Shin. "Ballistic quantum transport in nano-scale Schottky barrier tunnel transistors", 5th IEEE Conference on Nanotechnology, 2005., 2005  Publication                                                                                       | <1% |

| 12 | cfwebprod.sandia.gov Internet Source                                                                                                                                                                                                                              | <1% |

| 13 | Zhang, Shuang Yan, Jun Yu, Guang Fen Wei,                                                                                                                                                                                                                         |     |

Zhen An Tang, Yi Chen, and Yuan Hui Cui. "Gas Mixture Recognition Method with New Hybrid Architecture", Applied Mechanics and Materials, 2010.

<1%

Publication

Submitted to Nottingham Trent University

Student Paper

<1%

Hanene Ben Hammouda, Mongia Mhiri, ZiÃ"d Gafsi, Kamel Besbes. "Neural-Based Models of Semiconductor Devices for SPICE Simulator", American Journal of Applied Sciences, 2008

<1%

Peter B. L. Meijer, Christian Leistner, Anthony Martiniere. "Multiple View Camera Calibration for Localization", 2007 First ACM/IEEE International Conference on Distributed Smart Cameras, 2007

<1%

Publication

T. Feuring, A. Tenhagen. "Stability analysis of neural networks", Proceedings of International Conference on Neural Networks (ICNN'97), 1997

<1%

Publication

Exclude quotes

Off

Exclude matches

Off