# 1. JCTN2012

by Jatmiko Endro Suseno

**Submission date:** 18-Feb-2020 01:49PM (UTC+0700)

**Submission ID**: 1259394793

File name: 1.\_JCTN2012.docx (197.6K)

Word count: 1811

**Character count: 9525**

# Modeling of Drain Current for Grooved-Gate MOSFET

A drain current model of grooved-gate MOSFET, which is based on the difference of the channel depth distance along the channel from the source to the drain in cylindrical coordinate system, is presented in this paper. From the analysis, the potential of grooved-gate is related to geometry structure parameters, the angle  $(\theta_0)$  and the radius  $(r_0)$  of concave corner, as well as the channel depth (d). The presence of corner effect will influence the drain potential, drain current characteristics, and the other electrical characteristics, such as conductance  $(g_m)$  and transconductance  $(g_d)$ . In this result, our model shows the effect of corner along with an improvement in the device characteristics. In particular, the reduction of short channel effect (SCE) is shown. However, the drain current value of the grooved-gate MOSFET is slightly less than that of the ordinary MOSFET.

**Keywords:** grooved-gate MOSFET, curved channel, drain current model, Short Channel Effect (SCE), potential barrier.

#### 1. INTRODUCTION

The small geometry of conventional bulk silicon MOSFETs into the nanoscale regime has many problems associated with short-channel effects (SCEs). The grooved-gate MOSFET, which is created by corner region, offers a promising structure to reduce the Short Channel Effect. The influence of the corner effect may affect the potential barriers for the device channel [1-3] which can improve the characteristics of the device. Such improvement includes the reduction of short channel effect (SCE) such as a high threshold voltage roll-off ( $V_{th}$ ), a low DIBL and GIDL effect, closeness to ideal sub-threshold slope, and a high IoN-IoFF ratio [1-7]. An analytical numerical model of surface potential on Grooved-Gate MOSFET has been made using the 2D

Poisson equation method in cylindrical coordinates [I] in which the potential distribution function along channel,  $V(\theta)$ , relates to the grooved-gate MOSFET structural parameters  $(r_0, \theta_0, and d)$ , substrate doping and applied biases.

In this paper, we present a new drain current model for drain current characteristics of grooved-gate MOSFET, based on a determination of channel depth at its respective angle in the cylindrical coordinate system. The model is an approximation of the geometrical structure in the cylindrical coordinate system. It has a curved region geometry which is capable of accurately simulating the I-V characteristics of grooved-gate MOSFET. The dependence of I-V characteristics on corner radius  $(r_0)$ , corner angle  $(\theta_0)$ , channel depth (d), channel length (L) is shown in the paper.

#### 2. DEVICE STRUCTURES AND SIMULATION

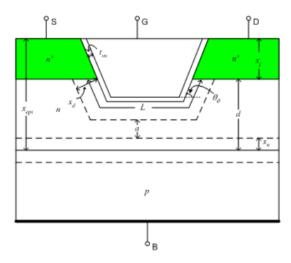

The grooved-gate MOSFET structure with depletion region is shown in Fig. 1. The gate electrode of device is located on a groove region separating the source and drain regions. In order to form the effective minus junction depth, the junctions of source/drain are made shallower than the groove bottom.

The presence of the groove in grooved-gate MOSFETs can enhance the electrical performance [8]. The curved structure at the channel of device is effective in reducing the electric field at the drain. Furthermore, it can also reduce the substrate current, and increase the voltage from gate to drain, thus improving the reliability of the device.

Figure 1: The Grooved-gate MOSFET structure

There are several geometrical parameters include in groove-gate MOSFETs such as channel length (L), junction depth  $(x_i)$ , the angle of the vertical concave sidewall structure  $(\theta_0)$ , and depletion depths of gate  $(x_d)$  and substrate  $(x_n)$ . These parameters can influence drain current value and others electrical performance, such as sub-threshold swing (S), minimum surface potential, DIBL and threshold voltage roll-off, etc.

#### 3. MODEL OF DEVICE STRUCTURE

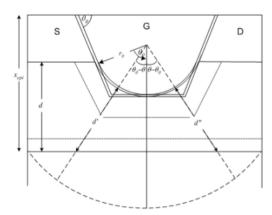

The grooved-gate structure of device can be approximated as the concave corner which is part of cylinder [1]. This device is shown in Fig. 2 below.

Figure 2: The Grooved-gate MOSFET with cylindrical approximation of concave corner

The variation of the parameters, such as the concave corner radius  $(r_0)$ , junction depth  $(x_j)$ , the angle of the concave gate structure  $(\theta)$  and the channel doping concentration can improve the performance and the short-channel effect (SCE). The electron potential profile in the channel region having concave corner, is derived by the Poisson equation in the cylindrical coordinates. The potential distribution function along the channel from analytical model solution [1] has been derived as:

$$V(\theta) = V_{BS} - \frac{M}{2x_{deff}} (V_g - \varphi_s(\theta))(R_2 - r)^2$$

(1)

Where M and  $x_{deff}$  are constant,  $M = \frac{C_{oxc}}{\varepsilon_{Si}}$  and  $x_{deff} = \sqrt{\frac{2\varepsilon_{Si}}{qN_A}1.5V_{bi}}$ , respectively, and  $C_{oxc}$  is

the gate oxide capacitance per unit area [1] of the corner region of the groove gate, with

$$C_{oxc} = \frac{\varepsilon_o \varepsilon_{ox}}{r_0 \ln \left(1 + t_{ox}/r_0\right)}$$

The modification of the potential equation at (1) using derivation of Poisson equation (as shown at Appendix A) and assumption of the potential equation  $V(\theta)$  at surface is surface potential  $\varphi_{\delta}(\theta)$ , we obtain:

$$V(\theta) = \frac{1}{Sinh\left(\frac{2\theta_0}{\lambda}\right)} \left[ \left(\Phi_s + V_d\right) Sinh\left(\frac{\theta}{\lambda}\right) + \Phi_s Sinh\left(\frac{2\theta_0 - \theta}{\lambda}\right) \right] + \zeta$$

(2)

where

$$\lambda$$

and  $\zeta$  are constants,  $\lambda = x_{deff} \sqrt{\frac{2}{x_{deff} - R_{\rm l}}}$  and  $\zeta = V_{\rm g} - \frac{N_{A}qx_{d}R_{\rm l}}{C_{\rm oxc}(x_{d} - R_{\rm l})}$ , respectively.

### 4. MODEL OF I-V CHARACTERISTICS

The equation of the I-V characteristics based on the difference of channel depth distance of the device is given by [10]:

$$I_{d}R_{1}d\theta = N_{D}q\mu_{eff}Wa(\theta)dV(\theta)$$

(3)

where W is the channel width,  $\mu_{eff}$  is the effective electron mobility,  $V(\theta)$  is the potential in the channel in the radial direction at angle  $\theta$ , and  $a(\theta)$  is the effective channel depth distance along the channel from the source to the drain and is given by:

$$a(\theta) = d' - x_n(\theta) - x_d(\theta) \tag{4}$$

where d' is the effective channel depth,  $x_d$  and  $x_n$  are the depths of depletion regions of the gate and the substrate respectively. This potential is zero at the source ( $\theta = 0$ ), and it is the value of  $V_d$  at the drain ( $\theta = 2\theta_0$ ).

The depth of the depletion region of the gate,  $x_d$ , is given by [9]:

$$x_d = \frac{\varepsilon_{Si}}{2C_m} \left( (1 + \delta(V_g - V(\theta)))^{1/2} - 1 \right)$$

(5)

where  $\delta$  is constant,  $\delta = -\frac{2C_{oxc}^2}{\varepsilon_{Si}qN_D}$ ,  $\frac{1}{N_D}$  is the channel doping,  $\theta$  is the electronic charge, and  $\varepsilon_{Si}$

is the permittivity of silicon.

The depth of depletion region of the substrate,  $x_n$ , is given by :

$$x_n = K_o \left( \phi_{bi} + V_B + V(\theta) \right)^{1/2} \tag{6}$$

where  $K_o$  is constant,  $K_o = \left(\frac{2\varepsilon_{Si}N_A}{qN_D(N_A + N_D)}\right)^{1/2}$ ,  $\phi_{bi} = (kT/q) \ln (N_AN_D/ni^2)$  is the built-in

potential,  $V_B$  is the substrate voltage,  $N_A$  and  $N_D$  are the acceptor and donor concentrations, respectively.

#### 5. I<sub>d</sub>-V<sub>d</sub> CHARACTERISTICS

From Fig. 2, the distance d between the bottom of the groove and the p-n junction of the source/drain boundary is:

$$d = x_{epi} - x_j \tag{7}$$

where  $x_{epi}$  is the thickness of the epitaxial layer and  $x_j$  is the junction depth of the source/drain n+diffusion.

The determination of effective channel depth distance is separate being two calculations due to the geometry of distance  $a(\theta)$  will increase from source to middle of channel and will decrease from middle of channel to drain as given by:

$$a(\theta) = \begin{cases} a'(\theta) = d' - x_d(\theta) - x_n(\theta) & 0 < \theta < \theta_0 \\ a''(\theta) = d'' - x_d(\theta) - x_n(\theta) & \theta_0 < \theta < 2\theta_0 \end{cases}$$

(8)

where:

$$d' = d Sec(\theta_0 - \theta) - R_1 Cos(\theta_0) Sec(\theta_0 - \theta) - R_1$$

, and  $d'' = d Sec(\theta - \theta_0) - R_1 Cos(\theta_0) Sec(\theta - \theta_0) - R_1$

The calculation of d and d can be seen at Appendix B.

The integration of drain current from eq (3) given as

$$I_{d} = \frac{N_{D}q\mu_{n}W}{2R_{l}\theta_{0}} \left[ \int_{V(\theta=\theta_{0})}^{V(\theta=\theta_{0})} a'(\theta)dV(\theta) + \int_{V(\theta=\theta_{0})}^{V(\theta=2\theta_{0})} a''(\theta)dV(\theta) \right]$$

(10)

From the above integration, we obtain the  $I_d$ - $V_d$  equation given as:

$$I_{d} = \frac{N_{D}q\mu_{eff}W}{2R_{1}\theta_{0}} \left[ \frac{V_{d}\theta_{0}}{2\lambda} \left( d - R_{1}Cos(\theta_{0}) \right) Csch \left( \frac{\theta_{0}}{\lambda} \right) \right]$$

$$+\frac{\theta_{0}}{\lambda}Csch\left(\frac{2\theta_{0}}{\lambda}\right)(dSec(\theta_{0})-R_{1})\left((\phi_{SG}+V_{d})Cosh\left(\frac{2\theta_{0}}{\lambda}\right)-\phi_{SG}\right)$$

$$-R_{1}V_{d}+\frac{V_{d}\varepsilon_{Si}}{C_{ox}}+\frac{\varepsilon_{Si}}{3C_{ox}\delta}\left(1-(V_{d}+\phi_{SG}-V_{g})\delta\right)^{3/2}-\frac{2}{3}K_{0}(V_{d}+\phi_{SG}+V_{g}+\phi_{bi})^{3/2}$$

$$-\frac{\varepsilon_{Si}}{3C_{ox}\delta}\left(1-(\phi_{SG}-V_{g})\delta\right)^{3/2}+\frac{2}{3}K_{0}(\phi_{SG}+V_{g}+\phi_{bi})^{3/2}\right]$$

(11)

where  $\varepsilon_{Si}$ ,  $\varepsilon_{\theta}$  are the permittivities of silicon and silicon dioxide respectively and  $t_{ox}$  is the oxide thickness along the walls of the groove,  $V_d$  is the drain voltage, and  $V_g$  is the effective gate voltage. The parameters  $K_{\theta}$  and  $\delta$  are the constants defined above.

The source-drain conductance  $g_d$  is the differentiation of  $I_d$  with respect to  $V_d$  and is given by:

$$\mathbf{g}_{d} = \frac{dI_{d}}{dV_{d}}\Big|_{V_{d}=0} = \frac{N_{D}qW\mu_{eff}}{2R_{1}\theta_{0}} \left(R_{1} + \frac{\varepsilon_{Si}}{C_{ox}} - K_{o}\sqrt{V_{bs} - V_{g} + \phi_{bi} + \phi_{SG}} - \frac{\varepsilon_{Si}}{2C_{ox}}\sqrt{1 - \delta(\phi_{SG} - V_{g})}\right) + \frac{\theta_{0}}{2\lambda} \left(d - R_{1}Cos(\theta_{0})\right)Csch\left(\frac{\theta_{0}}{\lambda}\right) + \frac{\theta_{0}}{\lambda} \left(dSec(\theta_{0}) - R_{1}\right)Coth\left(\frac{2\theta_{0}}{\lambda}\right) \right) \tag{12}$$

The transconductance  $g_m$  in the saturation region is the differentiation of  $I_d$  with respect to  $V_g$  in the saturation region:

$$g_{m} = \frac{dI_{d}}{dV_{g}}\Big|_{V_{d} = V_{ds}} = \frac{N_{D}qW \,\mu_{eff}}{2R_{I}\theta_{0}} \left(K_{o}\sqrt{V_{bs} + V_{ds} - V_{g} + \phi_{bi} + \phi_{SG}} - K_{o}\sqrt{V_{bs} - V_{g} + \phi_{bi} + \phi_{SG}} - \frac{\varepsilon_{Si}}{2C_{ox}}\sqrt{1 - \delta(\phi_{SG} - V_{g})} + \frac{\varepsilon_{Si}}{2C_{ox}}\sqrt{1 - \delta(V_{ds} + \phi_{SG} - V_{g})}\right)$$

(13)

#### 6. RESULT AND DISCUSSION

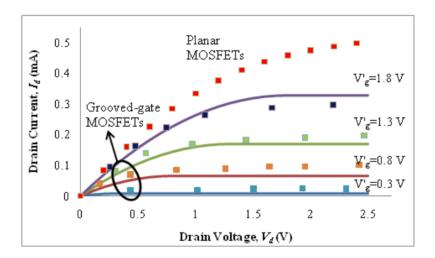

The  $I_d$ - $V_d$  characteristics can be obtained from equation (11) as shown in Fig. 3. This graph shows that the current drain reduction compared to the planar MOSFETs due to corner effect that effective in reducing the electric field. This also can decrease the substrate current, and increases the highest applicable gate to drain voltage, hence improving the reliability of the device. [3]

**Figure 3:**  $I_d$ - $V_d$  Characteristics of Planar and Grooved-Gate MOSFETs, with  $\theta_0$ =20° and  $r_0$ =1.2 nm

Some researchers have demonstrated an improvement in the drive current with some treatment.

One of them is using a hydrogen anneal at 800 °C that gives a 30% improvement in the drive current at 120-nm n-channel transistors [10].

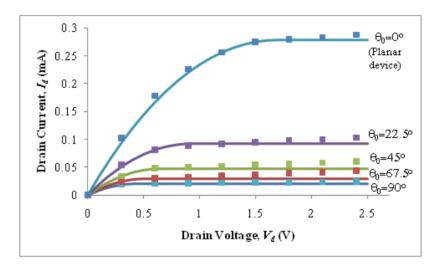

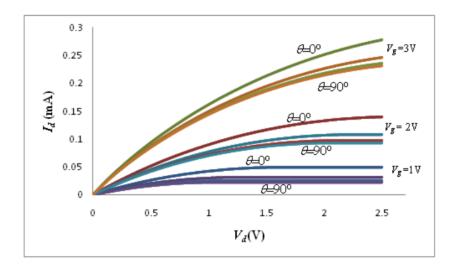

The drain current graphs of device with various concave corner angles are given in Fig. 4 and 5 for various  $\theta_0$  from  $0^{\circ}$  to  $90^{\circ}$ . The device with minimum angle of corner  $(0^{\circ})$  is like a planar device. These graphs show that the drain current decreases for a relatively larger corner angle.

**Figure 4:**  $I_d$ - $V_d$  graphs with various  $\theta_0$  (0°-90°) and  $V_g$ =1.3 V.

In other words, the presence of the corner effects can reduce the drain current because the potential barrier for electron flow from source to drain will increase and then the potential barrier which is effective in suppressing the short channel effect degrades the drain current characteristics as compared to the planar device.

**Figure 5:** Id-Vd graphs with various  $\theta_0(0^{\circ}-90^{\circ})$  and  $V_g(1\text{V}-3\text{V})$

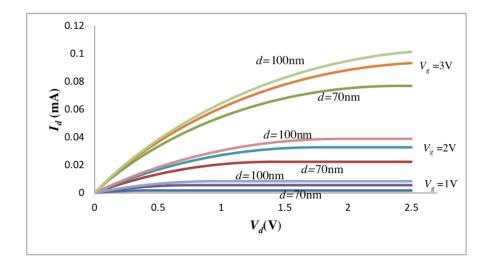

Figure 6 shows a typical set of I-V characteristic curves for the grooved-gate MOSFET geometry with various geometric channel depths d. The graph shows the drain current increase with a channel depth d increase for all gate voltage values. It means that for a device with the smaller d, it will be easy to compute MOS gate pinch-off and for higher d, the saturation of drain current does occur although the gate pinch-off may not occur.

Figure 6:  $I_d$ - $V_d$  Characteristics with various d(70nm-100nm) and  $V_g$ (1V-3V)

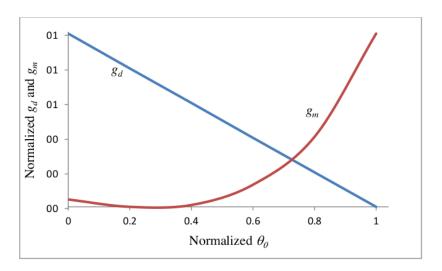

For the pinched-off devices, there are electrical characteristics measurements which include I-V characteristics, conductance below saturation, transconductance in the saturation region, pinch-off voltage and etc. For grooved-gate, the transconductance  $(g_m)$  and conductance  $(g_d)$  are very much correlated with device geometry, especially, the corner angle. The Figure 7 shows graphs of normalized transconductance  $(g_m)$  and conductance  $(g_d)$  with normalized angle of corner. The transconductance gm increases exponentially as the corner angle of device increases. In contrast with it, the conductance  $(g_d)$  decrease linearly when angle of corner increases.

Figure 7: The graphs of normalized of conductance  $(g_d)$  and transconductance  $(g_m)$

of device as various normalized  $\theta_0$

These results are obtained directly from solving equations (12) and (13) instead of using the modulation of normalized  $\theta_0$  which assumes that the effective channel length decreases with drain voltage increases beyond saturation when pinch off does occur.

#### 6. CONCLUSION

This drain current model of grooved-gate MOSFET is based on the channel depth distance along the channel using the 2D Poisson equation solution in the cylindrical coordinates. The structure includes some parameters, such as the concave corner radius, junction depth, the angle of the vertical concave sidewall structure and the channel doping concentration.

The result shows a reduction of the drain current due to the potential barrier from the implanted channel region and the curved structure. Furthermore, it is effective in reducing the electric field at the drain, thus improving reliability of short channel effects (SCEs), such as including subthreshold swing (S), minimum surface potential, DIBL and threshold voltage roll-off, etc. For the drain current reduction, it has been done using experiment of a hydrogen anneal at 800 °C that gives a 30% improvement of the drive current for the device.

#### **ACKNOWLEDGMENT**

The authors would like to thank the Research Management Centre (RMC) of Universiti Teknologi Malaysia (UTM) for providing excellent research environment in which to complete this work.

## 1. JCTN2012

#### **ORIGINALITY REPORT**

4%

SIMILARITY INDEX

INTERNET SOURCES

**PUBLICATIONS**

STUDENT PAPERS

#### **PRIMARY SOURCES**

Farzan, B.. "Depletion V-groove MOS (VMOS) power transistors", Solid State Electronics, 197604

Publication

S. Kimura, J. Tanaka, H. Noda, T. Toyabe, S. Ihara. "Short-channel-effect-suppressed sub-0.1-µm grooved-gate MOSFET's with W gate", IEEE Transactions on Electron Devices, 1995 Publication

2%

Hakim, M. M. A., A. Abuelgasim, L. Tan, C. H. de Groot, W. Redman-White, S. Hall, and P. Ashburn. "Improved Drive Current in RF Vertical MOSFETS Using Hydrogen Anneal", IEEE

Electron Device Letters, 2011.

%

Publication

Tong Jian-Nong, Zou Xue-Cheng, Shen Xu-Bang. "Influence of structural parameters on the immunity of short-channel effects in groovedgate nMOSFET", Chinese Physics, 2004

%

**Publication**

Exclude matches

Off

Exclude quotes

Exclude bibliography

Off

Off

# 1. JCTN2012

| 1. JCTN2012      |                  |  |

|------------------|------------------|--|

| GRADEMARK REPORT |                  |  |

| FINAL GRADE      | GENERAL COMMENTS |  |

| /0               | Instructor       |  |

|                  |                  |  |

| PAGE 1           |                  |  |

| PAGE 2           |                  |  |

| PAGE 3           |                  |  |

| PAGE 4           |                  |  |

| PAGE 5           |                  |  |

| PAGE 6           |                  |  |

| PAGE 7           |                  |  |

| PAGE 8           |                  |  |

| PAGE 9           |                  |  |

| PAGE 10          |                  |  |

| PAGE 11          |                  |  |